Цифровая техника

Справочная информация\Библиотека\Цифровая техника, программирование ПЛИС\Проектирование цифровых систем на VHDL

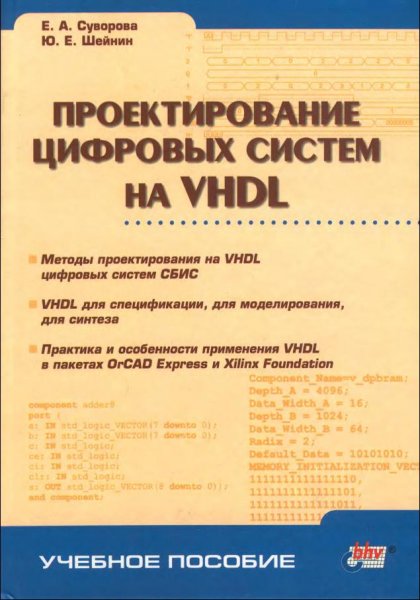

Проектирование цифровых систем на VHDL. Е.А. Суворова, Ю.Е. Шейнин., 2003г. - 13845 Кб

Название: Проектирование цифровых систем на VHDL

Авторы: Е.А. Суворова, Ю.Е. Шейнин

Издание: "БХВ-Петербург" - Санкт-Петербург, 2003

Формат: DJVU

Страниц: 565

Подробно, в полном объеме приводится язык VHDL, базовые конструкции моделей на этом языке, методы его применения, особенности VHDL для моделирования и для синтеза цифровых систем. Рассматриваются основы проектирования систем на СБИС, уровни и этапы проектирования СБИС и Систем-на-кристалле, использование VHDL в процессе проектирования цифровых систем — от начальной спецификации и моделирования до синтеза реализации в СБИС. Изложение иллюстрируется примерами моделей устройств на языке VHDL. Рассматривается шина АВМА АНВ, широко применяемая в Системах-на-кристалле, оцениваются ее характеристики. Приводится описание практической работы в популярных САПР — OrCAD Express и Xilinx Foundation Express — при проектировании на языке VHDL цифровых СБИС и Систем на кристалле. Для специалистов, разрабатывающих цифровые системы обработки и передачи информации, а также студентов и аспирантов, обучающихся по соответствующим специальностям Согласно известному эмпирическому правилу, так называемому закону Мура (Moore's Law), число транзисторов на кристалле СБИС (сверхбольших интегральных схем) удваивается каждые 18 месяцев (для процессорных схем). Это правило, сформулированное в 1965 году, когда на кристалле интегральной схемы размещалось всего 30 транзисторов, ко всеобщему удивлению, продолжает работать до сих пор (когда на кристалле процессорной СБИС размещается уже свыше 50 миллионов транзисторов!). Для логических СБИС к 2010 году прогнозируется миллиард транзисторов на кристалле. В некоторых СБИС — программируемых логических интегральных схемах (ПЛИС — FPGA), вполне доступных и отечественным разработчикам, уже содержатся миллионы вентилей. Возрастание сложности СБИС на базе развития интегральной технологии позволяет иметь в аппаратуре все большее число компонентов, схемотехнически реализовывать все более многообразные и сложные функции. Для эффективного использования этих возможностей необходим переход на новые технологии проектирования и применения аппаратно реализованных узлов, блоков, систем. Типичная логическая схема в графическом представлении содержит на странице фрагмент, эквивалентный порядку 200 вентилей. Соответственно, схема СБИС на 10 тыс. вентилей будет объемом в 50 страниц. Легко представить себе, во что выльется (по времени) составление и ввод в графической нотации схем СБИС сложностью 50 тыс., 100 тыс., 500 тыс. вентилей и далее. Альтернативой рисования детализированных схем из низкоуровневых элементов являются языки описания аппаратуры высокого уровня. Собирательно языки этого класса называют языками HDL (Hardware Description Language). Они не только обеспечивают компактную запись для проектируемой схемы, дают значительное сокращение трудоемкости и сроков разработки больших схем, но и упрощают миграцию, перенос проекта на разные варианты интегральных технологий, реализацию их в СБИС с учетом специфики технологий различных производителей. Разработчик получает возможность оценивать варианты реализации проектируемого устройства в СБИС при различных вариантах проектных ограничений, на различных технологиях, у различных производителей. Однако проблема не ограничивается только количественными характеристиками описания проектируемых схем. Используемые при разработке и применении аппаратуры традиционные схемы разных уровней (структурные, функциональные, принципиальные) являются как бы синтаксическим описанием аппаратно реализованных технических решений. Описание их работы, выполняемых функций традиционно дается словесно, с использованием привычных, но не стандартизированных и не всегда однозначных в понимании дополнительных графических форм (временных диаграмм и др.). Традиционные семантические формы спецификации функционирования цифровой аппаратуры — таблицы истинности, конечные автоматы, сети Петри и другие — оказываются пригодными для спецификации лишь очень небольших, по современным меркам, фрагментов аппаратуры. Используемые формы спецификаций не являются исчерпывающими, позволяют отразить лишь отдельные аспекты функционирования описываемой системы. Например, стандартных формализованных механизмов спецификации временного поведения аппаратно реализованных устройств просто нет. Некоторые специальные формализмы, типа темпоральной логики (temporal logic), не получили широкого распространения и в практике проектирования и эксплуатации аппаратуры не применяются. Используя традиционные средства описания аппаратуры, сложно получить целостное, достаточно строгое, однозначное описание современных многокомпонентных и функционально сложных цифровых систем. Возрастающая алгоритмическая сложность аппаратно реализованных устройств приводит к тому, что, как проблемы разработки, описания и применения аппаратуры (hardware), так и подходы к их решению, становятся подобны проблемам и методам решения для современных профаммных систем (software). Перспективное направление решения этих проблем — применение алгоритмического подхода, создание алгоритмического языка для описания аппаратуры, программирования и структуры, функционирования аппаратных средств обработки информации.

Язык VHDL предназначен для решения комплекса задач в ходе проектирования и применения цифровых систем, их аппаратных средств, в том числе:

1. Описания структуры системы, декомпозиции системы на подсистемы, спецификации связей и взаимодействия подсистем.

2. Спецификации функционирования системы, узлов, блоков, реализуемых функций. Спецификация дается в алгоритмической форме, с использованием привычных современному специалисту программных конструкций алгоритмического языка, включающих в себя спецификацию временного поведения сигналов и блоков.

3. Моделирования системы и ее работы на основе четкой спецификации структуры системы, а также функционирования ее компонентов.

4. Синтеза схемотехнической реализации системы, автоматической генерации детальной структуры на основе строгой спецификации системы на языке VHDL - спецификации на более абстрактном уровне.

Определив язык, мы получаем возможность писать на нем программы, то есть использовать его для описания структуры и функционирования системы (пункты 1 и 2 в приведенном перечне задач). Такое описание, достаточно формализованное и однозначное, будет уже иметь самостоятельную ценность, как средство передачи знаний о спроектированной аппаратно реализованной цифровой системе (устройстве, блоке) от разработчика к специалисту, ее применяющему. В этом качестве язык VHDL постепенно становится стандартным при документировании аппаратных средств, причем не только на уровне СБИС, но и на уровне плат и блоков. Высокий уровень описания проектируемого устройства на языке VHDL дает так называемый самодокументирующий характер описанию проекта. Текст программы на языке VHDL сам по себе является документацией, которую опытный специалист легко читает. Не случайно есть тенденция — в перечень необходимой документации на цифровые электронные блоки и устройства включать описание на языке VHDL. Так, Европейское космическое агентство (ESA) стандартизировало язык VHDL — и как средство обмена информацией при проектировании и применении заказных СБИС (ASIC), и как инструмент для работы на уровне конструктивно-функциональных модулей, аппаратных узлов на уровне плат. В отечественной промышленности также предполагается ввести документирование на VHDL как обязательную составляющую технической документации на изделия. HDL-языки составляют необходимую основу для развития методологии проектирования систем на СБИС с повторным использованием готовых компонентов, уже апробированных и отработанных на других проектах (такую методику называют устоявшимся словосочетанием design reuse). Основное внимание в настоящей книге уделяется этапам функционального и логического проектирования систем на СБИС. Именно с этими этапами имеет дело разработчик цифровых систем, реализуя заданные техническим заданием требования к проектируемой системе. Для заказных и полузаказных СБИС логический проект, сформированный разработчиком, поступает на схемотехническое и топологическое проектирование кристалла производителями СБИС. Однако, при реализации проектируемого цифрового устройства на FPGA (ПЛИС) — готовых кристаллов с фиксированной топологией, специальные формы схемотехнического проектирования для данного класса кристаллов, размещение реализации схемы на кристалле и трассировка также выполняются разработчиком систем на СБИС самостоятельно. Во всех вариантах реализации цифровых систем, современная технология проектирования СБИС базируется на использовании HDL-языков, прежде всего — языка VHDL. Рассматриваются общие принципы представления и проектирования систем на СБИС, основные классы СБИС, как элементной базы технической реализации проектируемых цифровых систем, типовые этапы разработки системы, место языка высокого уровня VHDL в этих процессах. Описываются базовые элементы языка VHDL, типы данных и операторов. Даются базовые конструкции языка VHDL для поведенческого и структурного описания проектируемого цифрового устройства. Акцентируется внимание на специальном классе объектов языка VHDL — сигналах, не имеющих аналогов в традиционных языках программирования. Излагаются методы использования конструкций языка VHDL для моделирования поведения, а также особенности программирования на VHDL для синтеза проектируемой системы на СБИС. Приводятся примеры использования языка VHDL при выполнении различных практических задач, решаемых при проектировании и применении систем на СБИС — от формализованной спецификации интерфейсов и протоколов, моделирования устройств, взаимодействующих по шине, до проектирования систем-на-кристалле. Рассмотрение ведется на примерах с использованием шины PCI на уровне блоков цифрового устройства и внут-рикристалльной шины АМВА (для систем-на-кристалле). Для того чтобы работать с программами на языке VHDL, выполнять их, требуется система программирования, которая бы проверяла корректность программы на данном языке, организовывала трансляцию, компоновку и выполнение оттранслированной программы при моделировании. Примером такой системы программирования для языка VHDL является программный комплекс семейства OrCAD — OrCAD Express, рассматриваемый в главе 6 (реализует задачи 1, 2 и 3). С другой стороны, при синтезе устройства, описанного программой на языке VHDL, пакеты проектирования должны выполнять трансляцию модели на VHDL, компиляцию аппаратной реализации устройства в кристалле СБИС. Для синтеза реализации проектируемых цифровых систем на FPGA используются специализированные пакеты сквозного автоматизированного проектирования с использованием языка VHDL (задачи 1, 2, 3 и 4). В качестве примера такого пакета в главе /описывается организация работы в пакете Foundation Express по проектированию цифровых систем на FPGA фирмы Xilinx. В приложениях приводится справочная информация, полезная при практическом проектировании систем на СБИС на языке VHDL. При подготовке книги использованы материалы курсов лекций, читаемых авторами в Санкт-Петербургском государственном университете аэрокосмического приборостроения.

Логический синтез реализации устройства

Синтез проектируемого устройства для его физической реализации в СБИС обычно выполняется поэтапно, несколькими компиляторами, синтезирующими программами, каждая из которых выполняет свой этап перевода с одного уровня представления проекта на другой (см. диаграмму Гайского-Канна). Предметом основного рассмотрения в данной книге является этап логического синтеза, с которым имеет дело разработчик устройств на СБИС. После этого этапа, дальнейшие стадии проектирования/синтеза выполняют уже другие специалисты — специалисты фирмы-изготовителя СБИС. Пакет Foundation Express, предназначенный для проектирования реализации устройств в FPGA, формирует реализацию устройства на вентильном уровне (gate level design), а также выполняет и ряд последующих этапов, но только для FPGA. Разрабатываемый на языке VHDL проект устройства вводится, редактируется, проверяется. На этом этапе многие современные пакеты автоматизации проектирования позволяют вводить описание структуры проектируемого устройства (или его частей) и в альтернативной форме — в графическом виде, в виде структурных схем. Такие пакеты, как рассматриваемые в данной книге пакеты OrCAD Express и Foundation Express, автоматически транслируют фафическое представление в структурное описание на языке VHDL и интегрируют его в общий проект на VHDL. При формировании проекта устройства на VHDL также активно используются библиотеки описания компонентов. Модель-спецификация проектируемого устройства на языке VHDL поступает на этап моделирования. На этом этапе производится функциональное моделирование проектируемого устройства, отладка проекта, формирование набора тестов и верификация на них устройства, спроектированного на языке высокого уровня. Отлаженная модель-спецификация проектируемого устройства на языке VHDL поступает на этап Логического синтеза, где производится преобразование проекта устройства с функциональной модели на языке высокого уровня на уровень логического проекта, представление проектируемого устройства на вентильном уровне1, т. е. на уровне, определяющем логическую схему устройства с учетом базиса реализации. На этом этапе выполняется и оптимизация логического проекта. Список связей (Netlist). Логическое описание на вентильном уровне, формируемое этапом логического синтеза, представляется уже не на языке VHDL, а в другой форме, называемой списком связей.

Комментарии к формату EDIF

В первой строке формата после ключевого слова edif указывается имя исходного объекта, для которого создавался список связей, затем указывается версия edif. И Foundation, и OrCAD используют одинаковую версию. Далее может идти статусная информация (время создания списка, программа, с помощью которой он был сгенерирован, путь к исходному файлу и др.). Собственно описание включает в себя описание компонентов, входящих в состав схемы. Каждый компонент называется ячейкой (cell). Для каждого компонента указываются наименования и направления портов. В качестве отдельных компонентов рассматриваются входные и выходные порты, компоненты, с помощью которых реализуется собственно схема. Вся схема тоже рассматривается как компонент. Далее идет описание цепей (net). Для каждой линии связи указываются порты компонентов, с которыми она соединена. Имена линий связи генерируются автоматически (в OrCAD и Foundation они формируются по-разному). В OrCAD и Foundation используются также различные библиотеки компонентов. Кроме того, в Foundation комбинационная схема сразу же отображается в LUT. В пакете Foundation Express, кроме формата EDIF, используется и собственный формат XHF, общий дня пакетов автоматизированного проектирования СБИС FPGA фирмы Xilinx, менее универсальный, но более компактный в представлении схем. Форматы кодирования списков связей, хотя и имеют читаемый вид, не предназначены для чтения и ручного анализа пользователем, а ориентированы на формирование и использование пакетами автоматизации проектирования СБИС. Мы приводим их примеры для общего представления разработчика о том, что кроется за широко применяемыми терминами список связей, netlist, EDIF, XNF и др.

Данные книги предоставлены исключительно в ознакомительных целях и должны быть

удалены с вашего компьютера или любого иного носителя информации сразу после

поверхностного ознакомления с содержанием.

Все авторские права на содержащийся в книге материал принадлежат правообладателю.

Без разрешения правообладателя материалы книги не могут быть использованы ни в

каких целях, кроме ознакомительных.

Публикация материалов данного типа не преследует коммерческих целей и является

рекламой бумажных аналогов (если такие существуют).

На данном сайте собраны лишь ссылки на литературу, имеющиеся в свободном доступе в сети интернет.

Комментарии